應材推兩大沉積系統搶攻2奈米製程 鎖定GAA電晶體助攻AI晶片效能

記者黃仁杰/台北報導

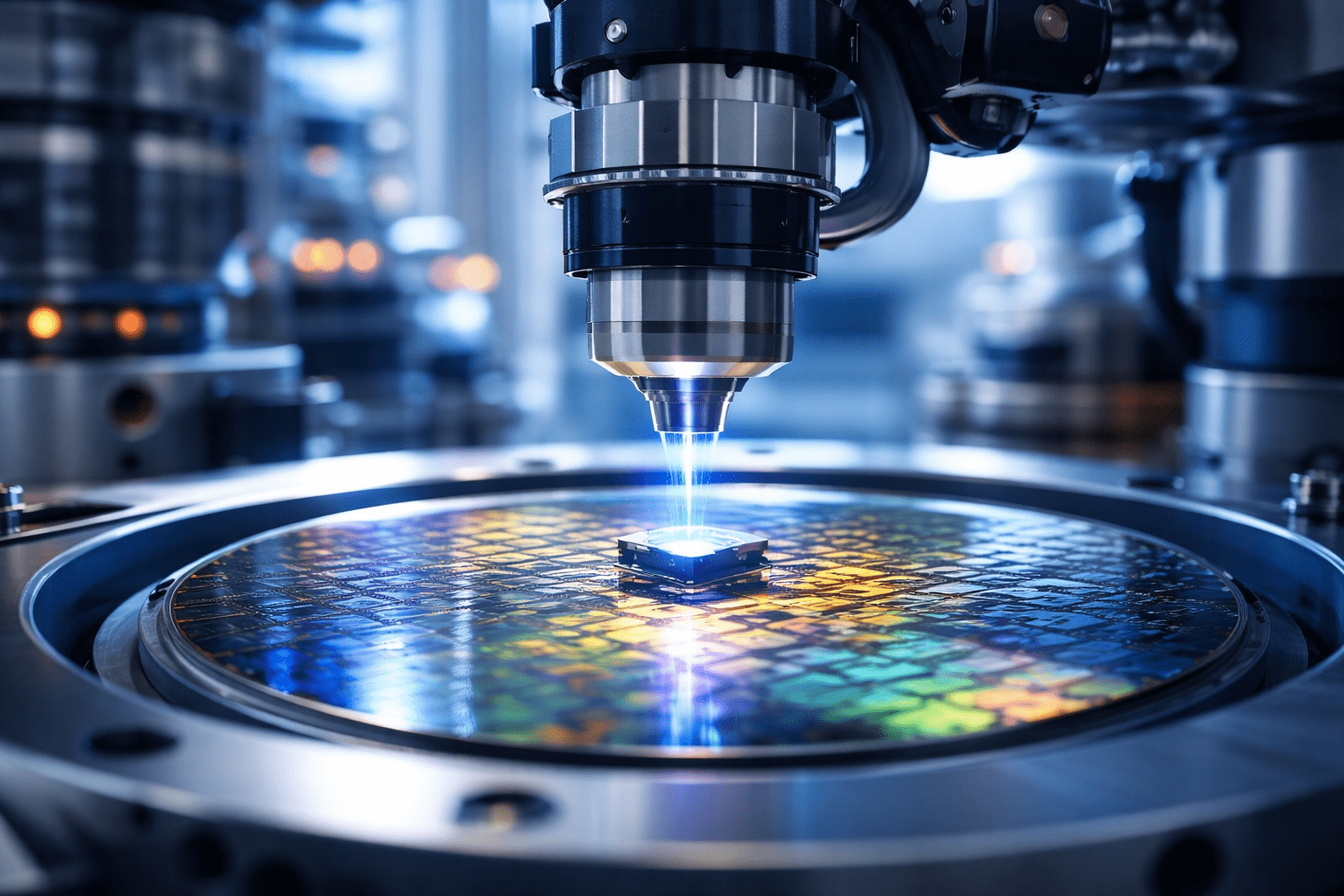

隨著AI運算需求快速攀升,半導體製程持續朝2奈米以下邁進,製程難度也大幅提高。應用材料今(14)日宣布,推出兩款全新晶片製造系統,主打在「埃米級」尺度下進行材料沉積,協助晶圓廠打造更高效、低功耗的先進邏輯晶片。

此次推出的系統,主要鎖定新一代電晶體架構Gate-All-Around transistor(GAA)。相較於既有技術,GAA可在相同功耗下提升效能,但製程複雜度大幅提高,單一晶片製造流程甚至超過500道步驟,對材料精準度與穩定性要求極高。

應材指出,在這樣的製程環境下,「材料工程」已成為決定晶片效能與功耗的關鍵,而非單靠微影技術即可突破。

解決漏電與功耗問題 Precision™鎖定電晶體隔離結構

其中一項重點產品為Precision™選擇性氮化矽電漿沉積系統,主要用於強化電晶體之間的「淺溝槽隔離」(STI)結構。

在高密度晶片中,若隔離效果不足,電子容易在電晶體之間干擾,形成寄生電容,進而拖慢速度、增加耗能。尤其在GAA架構下,元件尺寸更小,這個問題更加嚴重。

Precision™系統採用「由下而上」的選擇性沉積技術,只在需要的位置堆疊氮化矽,並以低溫製程避免損傷原有結構,有助於維持隔離完整性,降低漏電與功耗,提升整體效能。

更多科技工作請上科技專區:https://techplus.1111.com.tw/

科技社群討論區:https://pei.com.tw/feed/c/tech-plus

攻克奈米片包覆難題 Trillium™強化金屬閘極沉積

另一項關鍵技術Trillium™原子層沉積系統,則聚焦在電晶體核心的「金屬閘極堆疊」。

在GAA架構中,閘極需完整包覆僅約10奈米間距的矽奈米片,任何沉積不均都可能影響電晶體開關特性,進一步衝擊晶片效能與良率。

Trillium™透過高精度原子層沉積技術,能在極微小空間中均勻堆疊多層金屬材料,並整合多道製程於單一平台,讓晶片設計者可更靈活調整效能與功耗配置。

已導入2奈米製程 應材卡位AI晶片關鍵供應鏈

應材表示,這兩套系統已獲領先晶圓代工與邏輯晶片製造商採用,導入2奈米及更先進製程節點。

應用材料半導體產品事業群總裁帕布‧若傑(Prabu Raja)指出,半導體產業正進入非線性發展階段,材料創新將成為推動技術突破的核心動能,而相關沉積技術將直接影響AI晶片的發展進程。

![]()