Google傳攜手Marvell推雙晶片TPU計畫 直攻AI推論效能瓶頸

記者黃仁杰/編譯

Google擴大自研AI晶片布局,傳出正與Marvell Technology合作開發兩款新晶片,分別強化既有TPU架構與打造新一代AI推論專用處理器,企圖在ASIC市場重塑競爭格局。

根據外媒報導,雙方目前已展開合作洽談,規劃中的兩款晶片包括一款為與TPU搭配運作的記憶體處理單元(MPU),另一款則是全新設計、專為AI推論(inference)優化的次世代TPU。

MPU補強記憶體瓶頸 分擔TPU運算壓力

在架構設計上,MPU並非傳統TPU延伸,而是獨立的加速單元,主要負責處理記憶體相關運算,透過「記憶體內運算」(in-memory processing)降低主晶片負擔。

此類設計可有效分散資料傳輸與運算壓力,提升整體AI系統效率,尤其對大模型推論場景具關鍵意義。

更多科技工作請上科技專區:https://techplus.1111.com.tw/

科技社群討論區:https://pei.com.tw/feed/c/tech-plus

新一代TPU鎖定推論市場 對標GPU與ASIC競爭

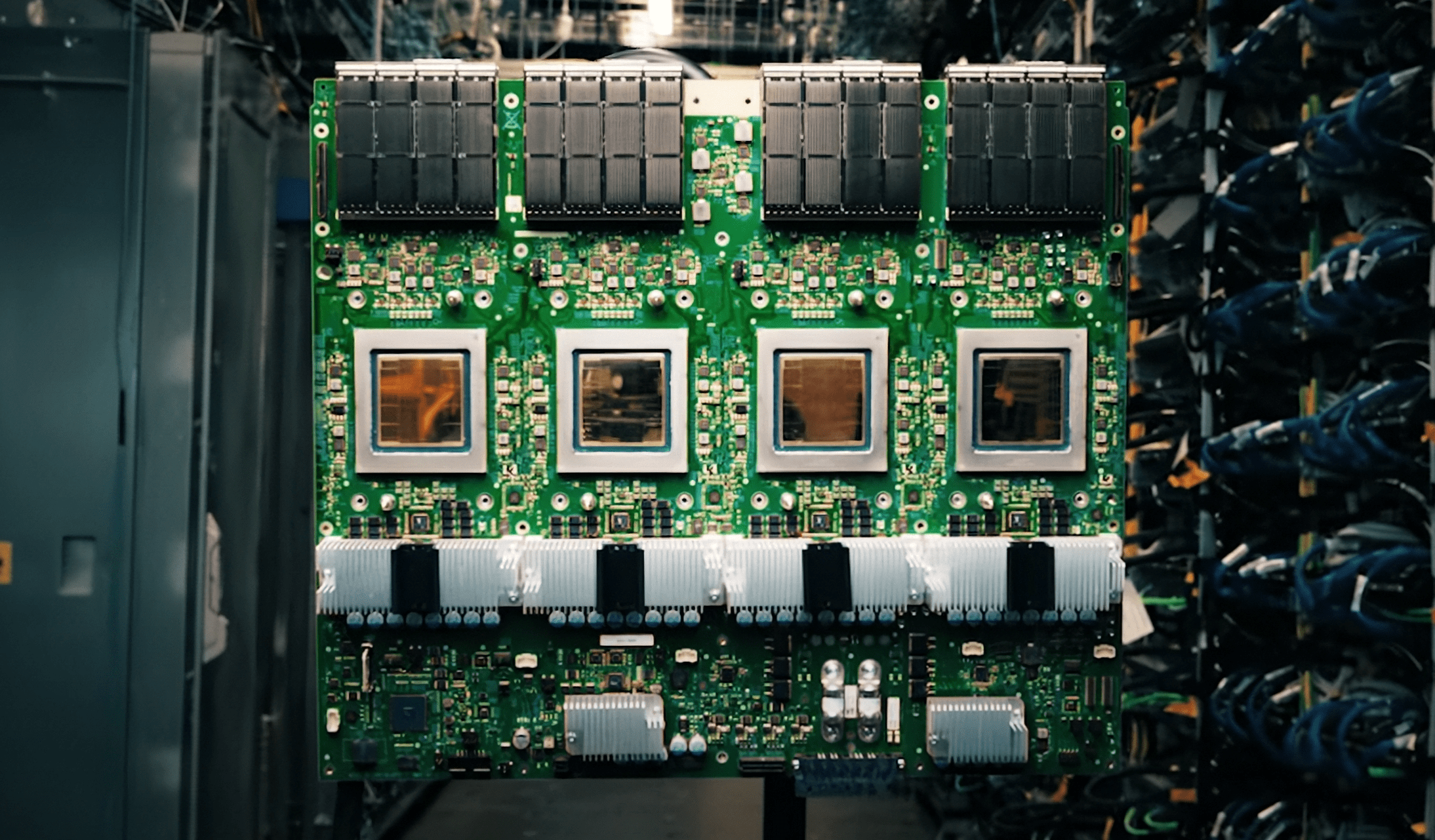

另一項重點則是新一代TPU,將針對AI推論進行深度優化。現行Google主力AI加速器為TPU v7(Ironwood),具備192GB高頻寬記憶體(HBM)、4614 TFLOPs運算效能,並整合於由9216顆晶片構成的Superpod系統中。

隨著企業對AI推論需求快速成長,專用ASIC晶片正成為關鍵戰場,Google此舉被視為強化自家TPU生態的重要一步。

供應鏈吃緊仍是挑戰 AI晶片需求持續爆發

儘管需求持續升溫,但半導體供應鏈產能仍面臨瓶頸。市場傳出,包括TPU在內的AI晶片產能已接近上限,成為限制發展的重要因素。

業界觀察,MPU的角色類似輝達推出的LPU(語言處理單元),例如Groq 3 LPX透過高頻寬SRAM設計,加速自主型AI(Agentic AI)運算。

AI推論進入新戰局 記憶體架構成關鍵

Google若順利推出「TPU+MPU」雙晶片架構,將有望突破記憶體瓶頸,顯著提升AI模型推論效率。

隨著AI應用從訓練轉向大規模部署,記憶體與資料流架構的重要性快速提升,晶片競爭也從單純算力比拼,進一步進入系統架構優化的新階段。

來源:wccftech

![]()