打造怪獸級處理器 台積電推突破性晶片技術

編譯/莊閔棻

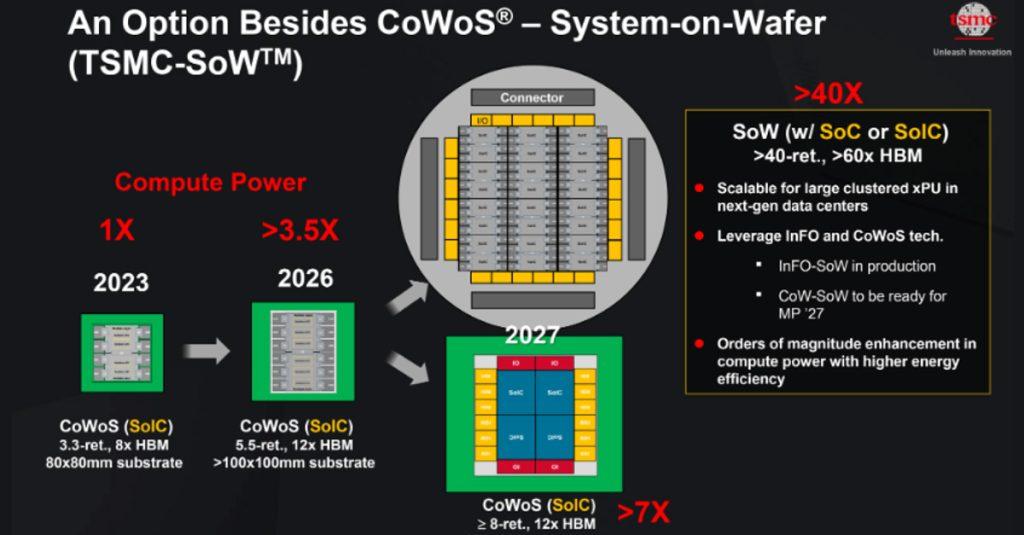

台積電在北美技術研討會上宣布,正在開發其晶圓上晶片(CoWoS)封裝技術的一個版本,使系統級封裝(SiP)的尺寸能增大兩倍以上,讓輝達的 B200 或 AMD 的 Instinct MI300X 處理器等現有巨頭相形見絀,台積電也討論了未來發展計畫。

120 x 120 毫米處理器

據報導,台積電新處理器的尺寸將達到 120 x 120 毫米,功耗高達千瓦。新 CoWoS 版本將使台積電能製造比以前更大的矽中介層,大約是858 mm²尺寸光罩的 3.3 倍,將邏輯IC、八個記憶體堆疊、I/O 和其他小晶片,安裝到高達 2831 mm² 的空間中。AMD的Instinct MI300X和Nvidia的B200都採用了這項技術,但輝達的B200處理器比AMD的MI300X更大。

100×100 毫米處理器

此外,台積電也指出,預計新一代 CoWoS將於 2026 年投入生產,能夠實現約 5.5 倍光罩尺寸的中介層,讓4719 mm² 版本將可包括邏輯IC、最多 12 個 HBM 記憶體堆疊和其他小晶片,可能使用約為 100×100 mm的基板,但這種大小限制也代表他們將無法使用 OAM 模組。

6,864 平方毫米的空間

台積電表示,到 2027 年,他們將擁有可以使中介層的尺寸達到光罩尺寸的八倍或更多倍的CoWoS ,為小晶片提供 6,864 mm² 的空間。台積電設想的其中一種設計依賴於四個堆疊式整合系統晶片 (SoIC),並與 12 個 HBM4 記憶體堆疊和額外的 I/O 晶片相配合。這樣一個龐然大物不但需要消耗巨大的功率,還要非常複雜的冷卻技術,並預計將使用 120×120 mm 基板。

CoWoS

台積電的CoWoS一直是人工智慧(AI)革命的關鍵驅動力,使客戶能將更多處理器核心和高頻寬記憶體( HBM)並排堆疊在單一中間設備上。同時,隨著系統整合單晶片(SoIC)已成為3D 晶片堆疊的領先解決方案,客戶越來越多地將CoWoS 與SoIC 和其他組件相結合,最大限度地提高系統級封裝整合度。

參考資料:itc.ua、Tom’s Hardware

![]()